Payment Method

2V~6V D-Typelocking Latch 8 14ns TSSOP-20 Latches ROHS

TSSOP-20Manufacturer:

Mfr.Part #:

74HC573PW,118

Datasheet:

Type Number:

74HC573PW

VCC (V):

2.0 - 6.0

Logic Switching Levels:

CMOS

Output Drive Capability (mA):

± 7.8

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

The 74HC573; 74HCT573 is an 8-bit D-type transparent latch with 3-state outputs. The device features latch enable (LE) and output enable () inputs. When LE is HIGH, data at the inputs enter the latches. In this condition the latches are transparent, a latch output will change each time its corresponding D-input changes. When LE is LOW the latches store the information that was present at the inputs a set-up time preceding the HIGH-to-LOW transition of LE. A HIGH on causes the outputs to assume a high-impedance OFF-state. Operation of the input does not affect the state of the latches. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of V.

| Type number | 74HC573PW | VCC (V) | 2.0 - 6.0 |

| Logic switching levels | CMOS | Output drive capability (mA) | ± 7.8 |

| tpd (ns) | 14 | Power dissipation considerations | low |

| Tamb (°C) | -40~125 | Rth(j-a) (K/W) | 100 |

| Ψth(j-top) (K/W) | 4.6 | Rth(j-c) (K/W) | 44.9 |

| Packing | SOT360-1_118 | Orderable part number | 74HC573PW,118 |

| Chemical content | 74HC573PW |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 5+ | $0.217 | $1.08 |

| 50+ | $0.175 | $8.75 |

| 150+ | $0.157 | $23.55 |

| 500+ | $0.135 | $67.50 |

| 2500+ | $0.121 | $302.50 |

| 5000+ | $0.116 | $580.00 |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for 74HC573PW,118, guaranteed quotes back within

[email protected],

or fill below form to Quote for 74HC573PW,118, guaranteed quotes back within

![]() 12hr.

12hr.

74LVC1G125GV

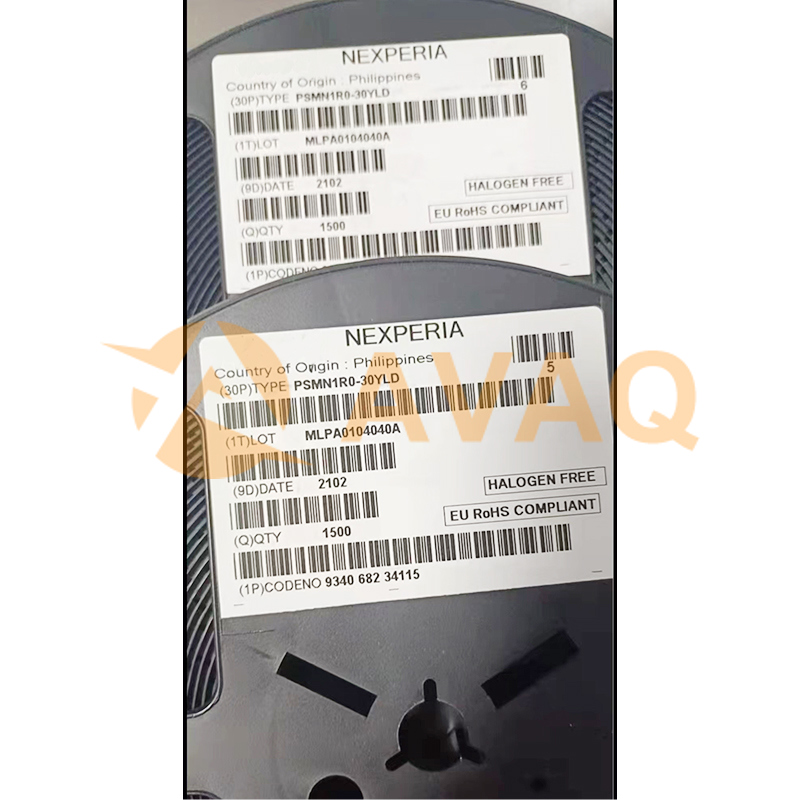

Nexperia

1000+ $1.033

74LVC1G125GW

Nexperia

Versatile non-inverting CMOS line driver

74LVC1G126GW

Nexperia

-state bus buffer line driver

IP4234CZ6

Nexperia

ESD TVS Diode for USB 2.0 in SOT-457 Package

74AUP1T34GW

Nexperia

Single-channel voltage level translator designed for automotive applications with a unidirectional signal flow