Payment Method

A3P600-FGG484 Field Programmable Gate Array

484-BGAManufacturer:

Microchip Technology

Mfr.Part #:

A3P600-FGG484

Datasheet:

Series:

ProASIC3

Programmabe:

Not Verified

Total RAM Bits:

110592

Number Of I/O:

235

EDA/CAD Models:

Send all BOMs to ![]() [email protected],

or fill out the form below for a quote on A3P600-FGG484. Guaranteed response within

[email protected],

or fill out the form below for a quote on A3P600-FGG484. Guaranteed response within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

Microchip Technology's A3P600-FGG484 FPGA is a standout choice for engineers and designers seeking a powerful yet versatile solution for their application needs. With a formidable 600,000 system gates, this FPGA offers ample capacity for complex logic configurations. What sets it apart is its innovative Flash*Freeze technology, which delivers exceptionally low static power consumption, making it an environmentally friendly option that also contributes to cost savings. The device's reprogrammable flash technology allows for in-system programming, enabling flexibility and adaptability in various scenarios. Equipped with 293 user I/Os, the A3P600-FGG484 provides extensive connectivity options, while its support for high-speed interfaces like SPI, I2C, and UART ensures seamless integration into diverse systems. Additionally, the FPGA's security features, including non-volatile key storage and anti-tamper capabilities, make it an ideal choice for applications that demand robust data protection. Whether it's in the communications, industrial, or automotive sectors, the A3P600-FGG484 stands as a reliable and cost-effective solution for designs requiring moderate logic capacity and programmability, setting a new standard for versatility and performance

| Series | ProASIC3 | Programmabe | Not Verified |

| Total RAM Bits | 110592 | Number of I/O | 235 |

| Number of Gates | 600000 | Voltage - Supply | 1.425V ~ 1.575V |

| Mounting Type | Surface Mount | Operating Temperature | 0°C ~ 85°C (TJ) |

| Base Product Number | A3P600 |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

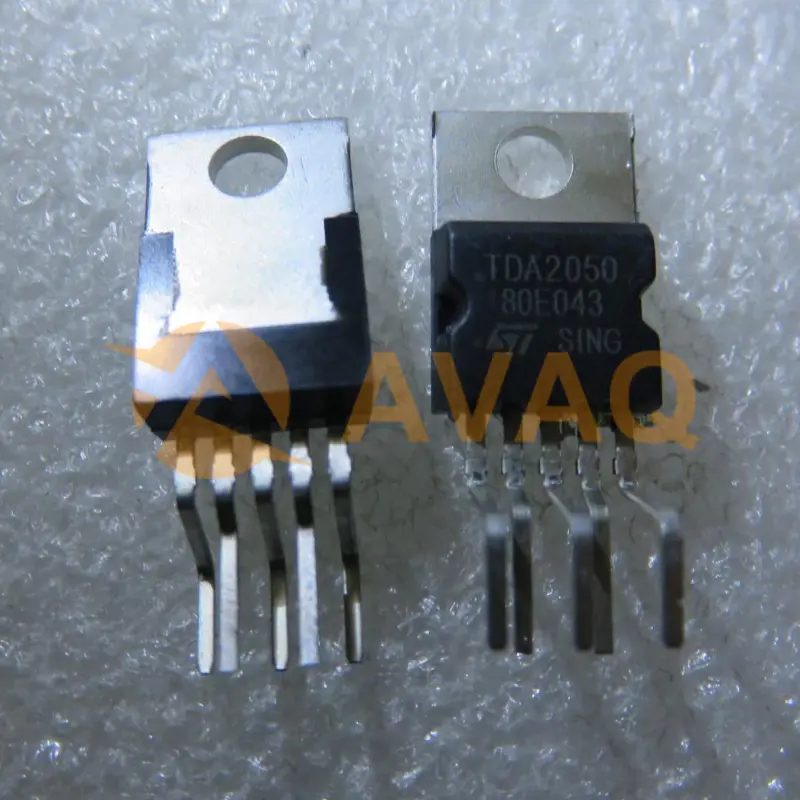

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power

DS1307+

Analog Devices

I2C DIP-8 Real-time Clocks (RTC) ROHS