Payment Method

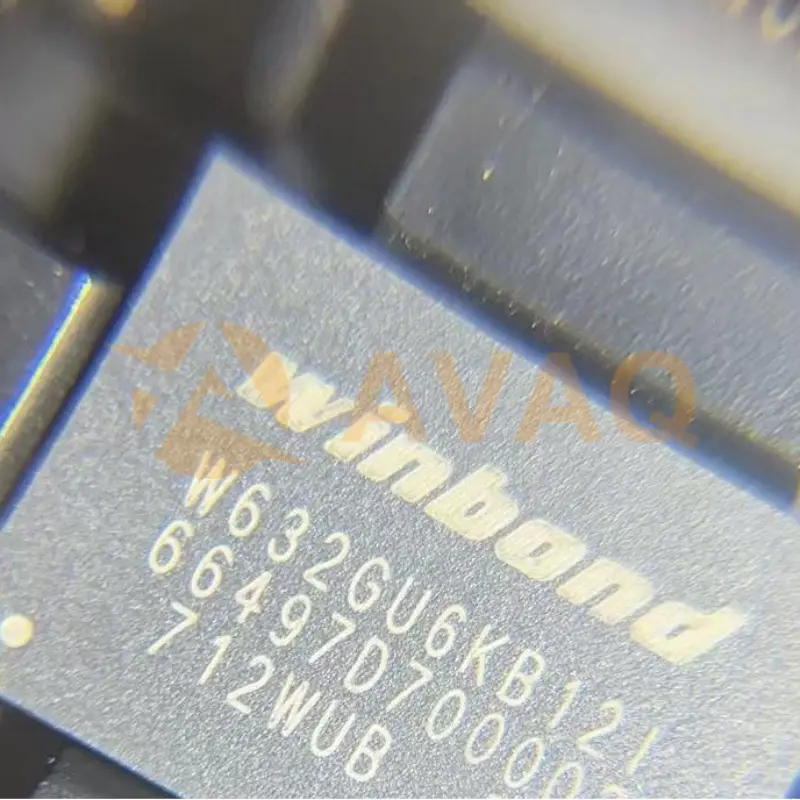

2Gbit DDR3L SDRAM

96-WBGA (9x13)Manufacturer:

Winbond Electronics

Mfr.Part #:

W632GU6KB12I

Datasheet:

Part Life Cycle Code:

Active

Pin Count:

96

Reach Compliance Code:

compliant

ECCN Code:

EAR99

EDA/CAD Models:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for W632GU6KB12I, guaranteed quotes back within

[email protected],

or fill below form to Quote for W632GU6KB12I, guaranteed quotes back within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

Automotive manufacturers looking to enhance the performance of their onboard systems can trust the W632GU6KB12I chip to deliver reliable and fast data storage capabilities. Its DDR4 SDRAM technology ensures quick access to critical information, while the low-power design helps conserve energy without compromising on speed or capacity. Whether it's for infotainment systems, navigation tools, or advanced sensor networks, this memory chip excels in demanding automotive applications where quality and efficiency are paramount

| Part Life Cycle Code | Active | Pin Count | 96 |

| Reach Compliance Code | compliant | ECCN Code | EAR99 |

| HTS Code | 8542.32.00.36 | Access Mode | MULTI BANK PAGE BURST |

| Additional Feature | AUTO/SELF REFRESH | I/O Type | COMMON |

| Interleaved Burst Length | 8 | JESD-30 Code | R-PBGA-B96 |

| Memory IC Type | DDR3L DRAM | Memory Organization | 128MX16 |

| Memory Width | 16 | Number of Functions | 1 |

| Number of Ports | 1 | Number of Terminals | 96 |

| Number of Words Code | 128000000 | Operating Mode | SYNCHRONOUS |

| Output Characteristics | 3-STATE | Peak Reflow Temperature (Cel) | NOT SPECIFIED |

| Refresh Cycles | 8192 | Self Refresh | YES |

| Sequential Burst Length | 8 | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | INDUSTRIAL |

| Terminal Form | BALL | Terminal Position | BOTTOM |

| Time@Peak Reflow Temperature-Max (s) | NOT SPECIFIED |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.